隨台積電不斷擴廠,對於晶圓的效能需求越來越高,測試市場責任也越來越大,成為公司降低生產成本的關鍵之一。

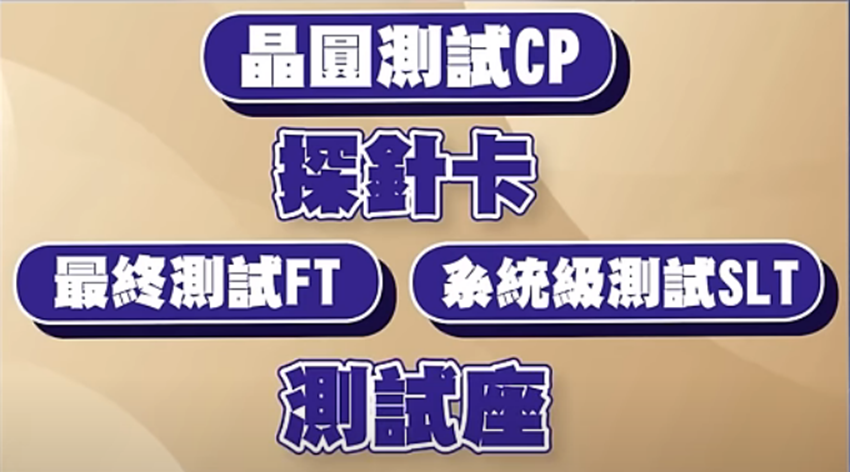

晶片在測試階段上分為CP,FT與SLT,CP主要是在wafer階段就先根據晶粒做區分,分為good die與待測晶粒。

而FT是Final Test的縮寫,指的是晶片在封裝完成以後進行的測試,檢測整體晶片經過封裝過程是否有出現不良訊號。

最後SLT又稱為系統級測試,開始運用外部干擾來衡量整體晶片的極限,像是耐熱性,高電壓穩定性等。

所以SLT系統級測試能模擬實際終端應用的場景,透過運行程式來檢驗晶片的良率,此方式亦能補足以往CP、FT 測試覆蓋率(Coverage Rate)不足的問題。

所以每個步驟都有其專業領域,像是精測與旺矽主打CP測試,而雍智與穎崴主打較後段的FT測試,至於京元電子則包含FT、Burn-in test(老化測試)與SLT(系統級測試)。

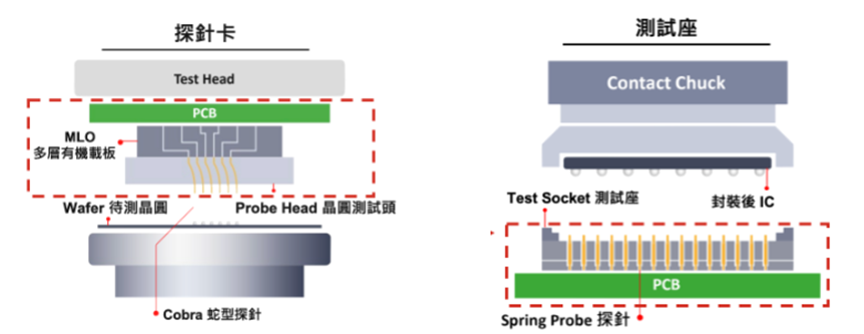

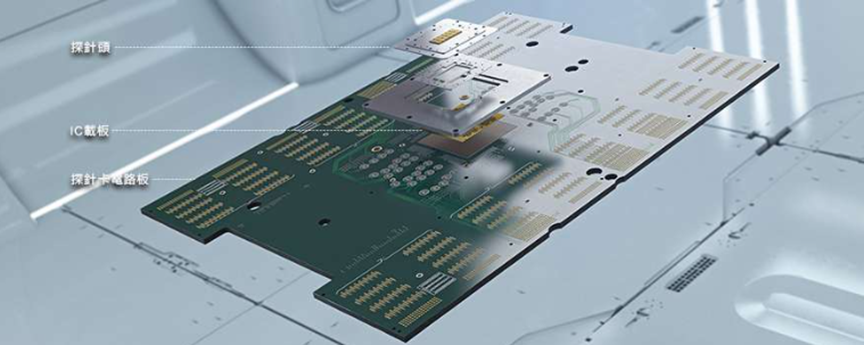

探針卡與測試座示意圖

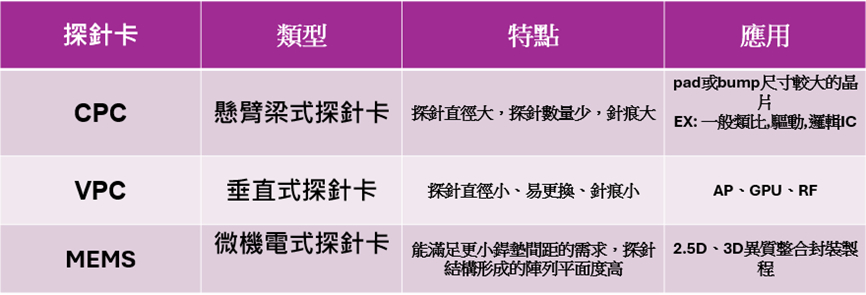

CP在測試過程所使用的設備是探針卡,可分為懸臂樑式探針卡CPC(Cantilever Probe Card)、垂直式VPC(Vertical Probe Card)、與微機電式MEMS(Micro Electromechancal System, MEMS)等不同模式之探針卡。

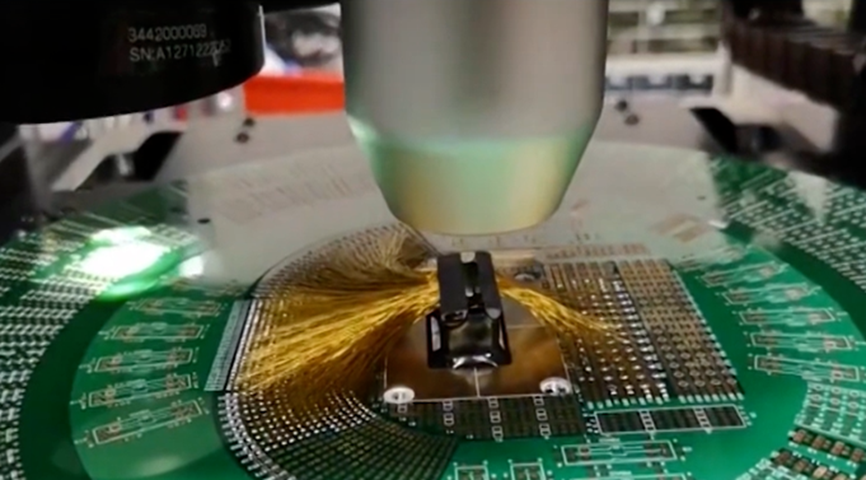

懸臂式探針卡如下

探針卡(CPC)其主要結構包含印刷電路板(PCB)、探針(Needle)、環氧樹酯(Epoxy)和環型基座(Ring)等四部分所構成。

而隨著AI晶片需要快速且強大的運算能力,不僅是在探針卡上要求越高,對於PCB版的層數也越高,而旺矽也可開始自行開發測試用PCB版。

所以我們可以知道隨著台積點產能擴充,不只影響封裝測試,也關係著上游PCB板,彼此都有關聯不可忽略之。