隨著AI浪潮引爆,CoWoS產能不足成為供需關鍵,更有法人將原先預估明年底的CoWoS月產能從4.5萬上修到6萬,更有市場預估台積電明年先進封裝將調漲10%-20%。

在半導體產業中,後段製程的封裝與測試的關係密不可分,因為在封裝之前,需要先對未封裝的電子晶片進行電性測試,以篩選出不合格的晶片,而封裝後則需要對完成封裝的晶片進行功能性及環境測試。

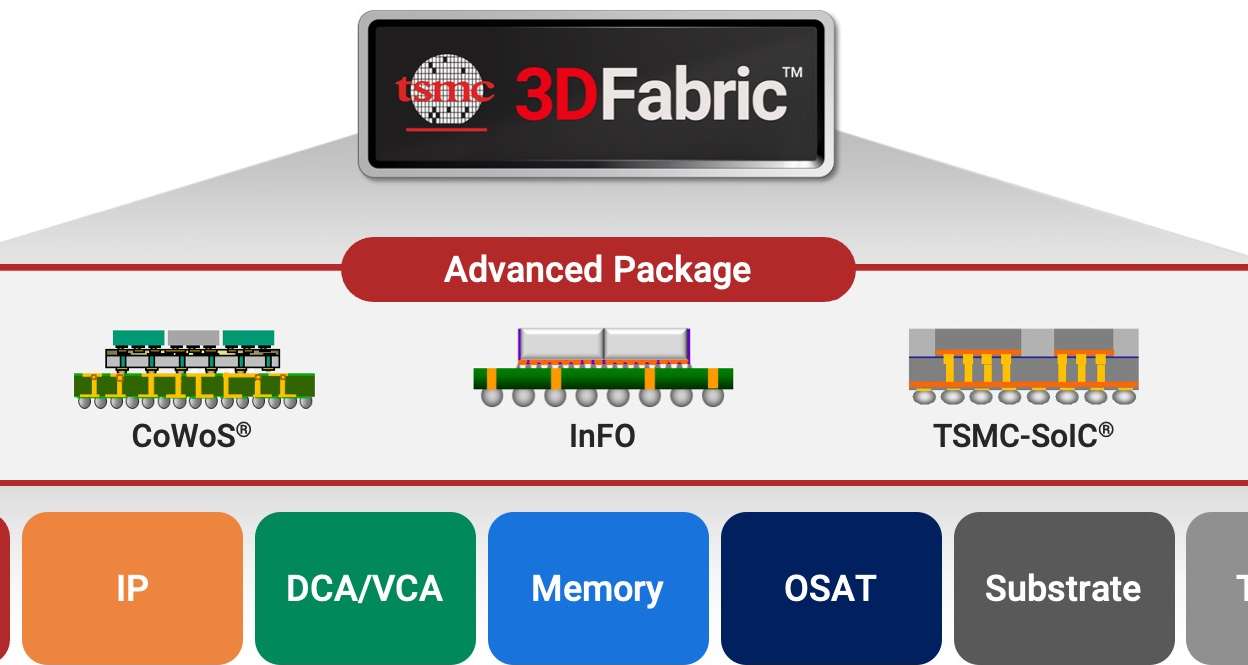

先進封裝的關鍵技術有哪些?

凸塊 (Bump):傳統封裝主要依賴引線連結,而先進封裝是透過在晶片上形成微小的金屬凸塊連接。隨著先進封裝技術的進步,縮小了晶片封裝的密度以及體積,Bump的尺寸和間距也隨之變小。

(圖片來源:艾邦半導體網)

重布線層 (Redistribution Layer,RDL):是用於在晶片或晶圓表面上增加額外的金屬層,以重新分配和優化電路互連布局,RDL可以將晶片的輸入/輸出 (I/O) 引腳重新布置到所需的位置,從而提高封裝的靈活性和性能。

(圖片來源:電子發燒友)

矽穿孔 (Through Silicon Via,TSV):TSV是透過晶片與晶片之間、晶圓和晶圓之間製作垂直導通,TSV技術是透過銅、鎢、多晶矽等導電物質填充。

(圖片來源:電子發燒友)

晶圓級封裝 (Wafer-Level Packaging,WLP):是將整個晶圓封裝完成後,在切割成晶片,這種技術可以減小封裝尺寸,並提高封裝效率。

(圖片來源:電子發燒友)

結論

與傳統封裝相比增加不少關鍵的技術,因此出現一個新名詞為中段製程,主要為晶圓級封裝的設備以及材料供應鏈,由於前段製程設備多為國外設備廠主導,中後段製程設備為台廠可望切入的新機會。