全球半導體邁入後摩爾定律時代、AI 與高效能運算 (HPC) 需求急遽,國科會主委吳誠文表示,未來的 AI 應用,需更高效能、更高密度、同時更低功耗的晶片解決方案。國科會旗下的「國研院半導體中心」今 (13) 日發表「晶片級先進封裝研發平台」,不僅提出去除基板的 CoCoB 封裝架構,該基板不僅能降低基板成本與製程複雜度,將助力台灣邁向以系統整合與應用創新的半導體競賽。

「先進封裝技術」不只是下一代半導體競爭的核心戰場,更將決定台灣未來的科技領導地位,國研院半導體中心開發的「晶片級先進封裝研發平台」,不僅為台灣產學研界提供全球獨特的晶片級先進封裝研發能力,更將催生一個屬於台灣的「先進封裝創新生態系」,加速前瞻實體 AI 技術的落地與商業化,帶動百工百業升級。

國研院表示,隨著製程微縮逐漸逼近物理極限,傳統以單一大型晶片為核心的系統單晶片 (SoC) 設計,已難以全面回應 AI 與 HPC 對於高速運算、超高頻寬與低功耗的需求,以異質整合為核心的先進封裝技術應運而生,透過將處理器、記憶體、高速傳輸等不同功能的小晶片,將如同樂高積木般進行 3D 封裝整合。

目前全球量產最先進的封裝技術之一為台積電 (2330-TW) 的 CoWoS,透過中介層晶圓與基板,實現運算晶片與高頻寬記憶體的高密度整合。而基板層的存在,也帶來成本、訊號傳輸距離與製程複雜度的挑戰。

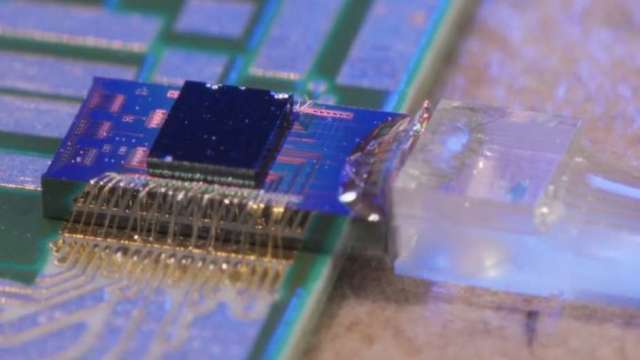

CoCoB 封裝架構,該技術省略傳統基板,直接將中介層晶片與電路板連接,其難度猶如將一片很大片的鋼化玻璃,放置於鋪滿鵝卵石的地面上,卻仍需確保每一個接觸點都能精準連接,半導體中心透過在每一微小連接球下方導入可流動介面材料,成功克服不平整問題,使所有連接點皆能可靠接合。

此 CoCoB 技術具備兩大優勢:一是大幅縮短訊號傳輸路徑,顯著提升整合密度與系統效能;二是降低基板成本與製程複雜度,特別適合學研單位與新創團隊進行高彈性、低成本的異質整合實驗。產業界認為這種「去除基板」的封裝架構,將是下一代 AI 晶片的重要發展方向。

國研院表示,長期以來,全球先進封裝產能供不應求,讓學研界與新創團隊難以取得最前沿的封裝資源,國研院半導體中心此次建置的「封裝研發平台」,正是以國家級科研能量,補上台灣半導體創新體系中最關鍵的一塊拼圖。

※ 本文經「鉅亨網」授權轉載,原文出處