隨著台積電製程越精細,對於下游合作的封裝與PCB的挑戰也越大,主要像是封裝傳導的針腳導線架,數量也隨效能越高變得越來越精細。

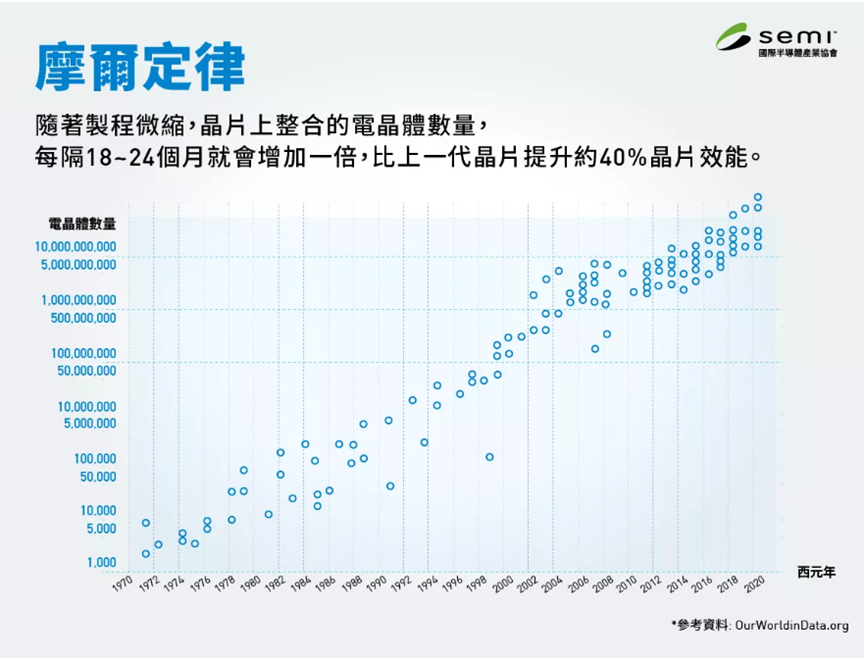

另外隨摩爾定律,台積電電晶體不斷縮小,最終還是會到達物理極限,也就是同一塊面積每隔2年,電晶體的數量會增加一倍,所以相對電晶體的面積每隔2年就必須縮小一倍,如此一來才能夠維持每年效率的提升。

所以在封裝廠與PCB廠面臨製程微縮挑戰時,台積電又想要不斷進步提高效能之下,唯一的解方就是3D封裝,由原本不斷微縮面積,變成直接在晶圓運用矽穿孔賦能,除了能讓相關供應鏈能夠喘口氣外,台積電效能也能如願提升。

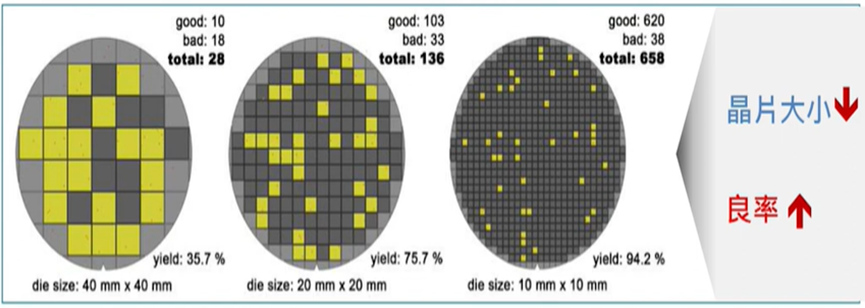

除此之外,由於晶粒大小與良率成反比,由下圖可知,當4CM x 4CM晶粒時,黑色好的晶粒約有10顆,良率為35.7%,但若是用1cm x1cm的晶粒,好的部分可以達到620顆,良率可以提升至94.2%。

圖片來源:富邦證券

除了成本與良率的好處外,與其在一塊大面積上塞很多功能,不如把很多不同功能的小晶片組合起來,可以提高設計彈性,這個概念就叫做chiplet。

圖片來源:富邦證券

Chiplet的優勢在於升級更新時,可以針對需要升級的區塊進行更新,若是要擴充新功能,也能夠在不妨礙到其他功能下進行額外擴充,進而加速產品上市週期。

圖片來源:富邦證券

所以整個晶片開始以小晶片chiplet為主的趨勢下,對於先進封裝與探針卡等測試需求將會逐漸提升,相關概念股均有機會成為長期未來的趨勢。

圖片來源:富邦證券