隨著半導體前段製程的微縮面臨技術和成本挑戰,為了繼續提升單位面積的電晶體數量,晶圓代工廠和封測廠正共同推動先進封裝技術的發展。

先進封裝就是將不同種類的晶片透過封裝、堆疊技術整合在一起,以提升晶片的性能、縮小尺寸、減少功耗。

先進封裝的種類有哪些?

依封裝平台的類型,先進封裝可分為覆晶、扇出型、扇入型、2.5D/3D、嵌入式裸晶等。

-

覆晶(Flip-Chip):是通過將晶片連接到銲錫凸塊(Solder Bump),然後將晶片翻轉,使凸塊直接與基板(substrate)連接。

-

扇出型(Fan-Out Wafer-Level Packaging,FOWLP):將晶片置於一個臨時載體上,並通過再分佈層將互連引出晶片範圍外,形成扇出結構,從而增加I/O引腳數量和密度。

-

扇入型(Fan-In Wafer-Level Packaging,FIWLP):所有的互連都集中在晶片範圍內,適合I/O數量較少的晶片。

-

2.5D/3D:使用中介層(interposer)將多個晶片連接在一起,再利用TSV等連接技術將其垂直連接。

-

嵌入式裸晶(Embedded Die):將晶片嵌入到基板材料中,有助於縮小封裝厚度和提升熱性能。

終端應用推動先進封裝發展,先進封裝將於2025年成為主流

隨著電子產品對性能不斷的追求,如高效能運算、網路通訊和消費性電子等應用需求將促使先進封裝技術往大面積、更高I/O密度發展。

根據Yole Group數據顯示,2023年全球封裝市場規模為940億美元,其中先進封裝市場占比50%,預期先進封裝佔整體封裝市場的占比將於2025年超過傳統封裝來到51.03%,並於2028年先進封裝市場規模將上升至786億美元,先進封裝市場占比將達到55%,年複合成長率(CAGR)達10.05%。

先進封裝新技術-SoIC

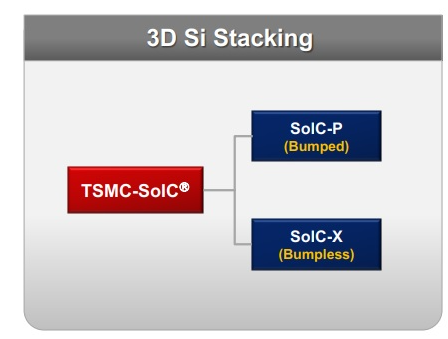

NVIDIA引爆AI浪潮之下,CoWoS產能需求激增,驅使台積電積極擴充CoWoS產能,除了CoWoS之外,台積電還有另一個3D先進封裝技術-SoIC(System-on-Integrated-Chips)。

SoIC(System-on-Integrated-Chips)是業界第一個高密度3D小晶片堆疊技術,用於十奈米及以下的先進製程進行晶圓級的鍵合技術。

而SoIC有兩種堆疊方案,分別為SoIC-P(Bumped)和 SoIC-X(Bumpless) 。

SoIC-P 是微凸塊堆疊解決方案,適用於行動應用等講求成本效益的應用。

另一種 SoIC-X是採 Hybrid Bonding(混合鍵合),適合用其 HPC、AI 領域。

(資料來源:台積電)

而且SoIC技術還可以和CoWoS技術以及和InFO技術結合,將SoIC晶片替代原先SoC晶片,使其在同樣的空間大小內,可以提升晶片的傳輸速度並且降低功耗以及成本。

(資料來源:台積電)

結論

隨著半導體前段製程的微縮面臨技術和成本挑戰,為了提升單位面積的電晶體數量,晶圓代工廠以及封測廠共同推動先進封裝技術的發展,再加上終端應用的需求驅使先進封裝技術往更大面積及更高I/O密度發展,由此可預期先進封裝產業後續的成長性是可以期待的。