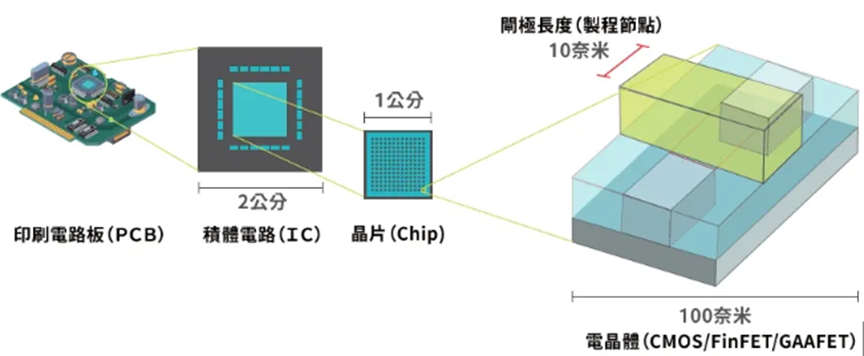

封測=封裝+測試,兩者都有其獨到的工藝,隨運算效率需求不斷提升,IC越做越小,加上摩爾定律指出當電晶體微縮到一定程度後,終有一天會達到物理極限,所以想要打破摩爾定律持續提升算力,封裝技術成為關鍵。

圖片來源:散冊

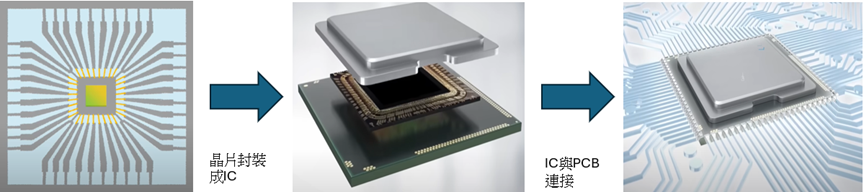

所以隨著台積電製程越來越先進,針腳數量複雜度逐漸提昇,讓封測廠甚至PCB廠也不得不跟上腳步,而IC 封裝主要可以分成兩個部份:IC 與 IC 載板間的連接、IC 載板與 PCB 板之間的連結。

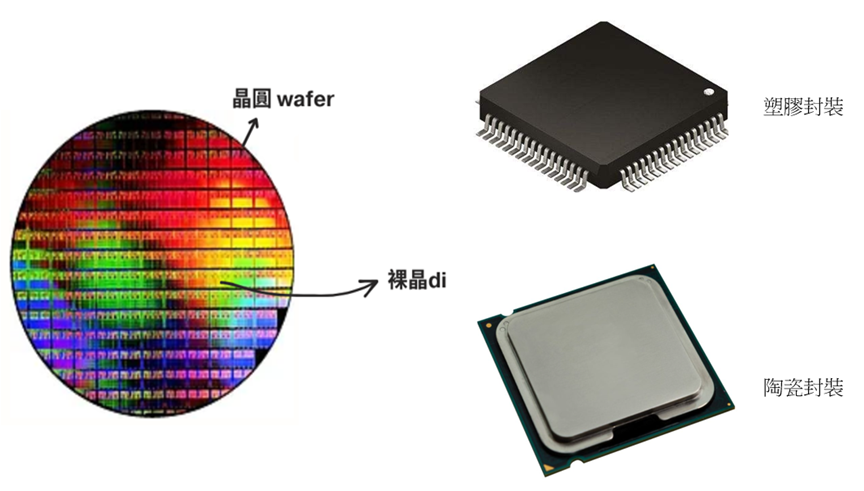

由於晶圓(wafer)上有很多方型的裸晶(die),它們極其脆弱,所以需要靠封裝保護,以避免碰撞與水氣破壞,而封裝材質包含塑膠與陶瓷。

一般來說家用電器,環境較為穩定的地方,會使用一般的塑封,但像是電動車或是軍事衛星等環境與安全度要求較高的,就會使用陶瓷封。

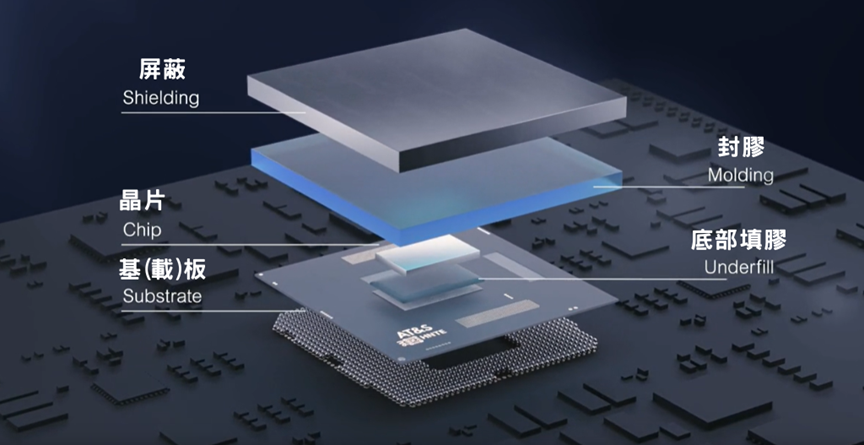

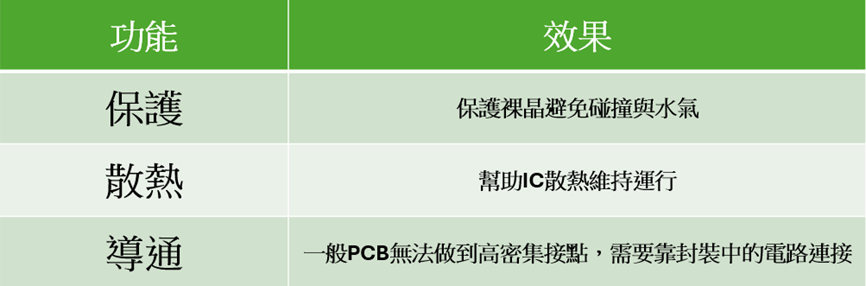

而封裝的主要功能具有保護、散熱與導通,下圖當中填充的一層Molding具有隔絕濕氣與散熱效果,而shielding則具有保護效果。

封裝後的IC變得更加耐用,並且在上面接上可以與 PCB 板導通的材料,達到訊號傳輸,整體賦能。

圖片來源:經濟部技術處

圖片來源:經濟部技術處

而所謂的「先進」封裝,其實想到的會是台積電而非傳統封測大廠,因為先進封裝已經面臨到 7nm 以下,而傳統封裝廠研發速度已無法跟上晶圓製程的腳步。

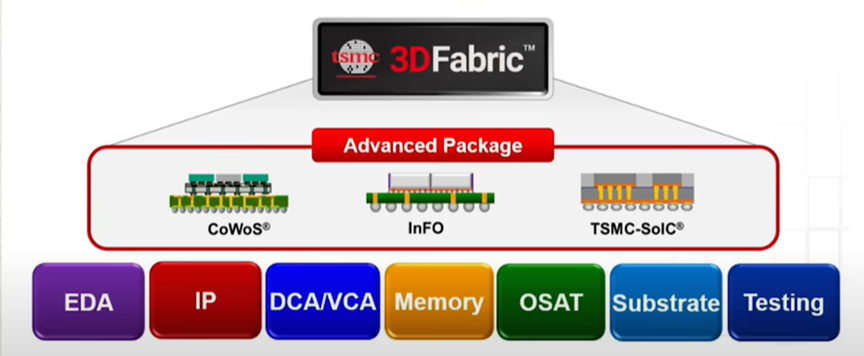

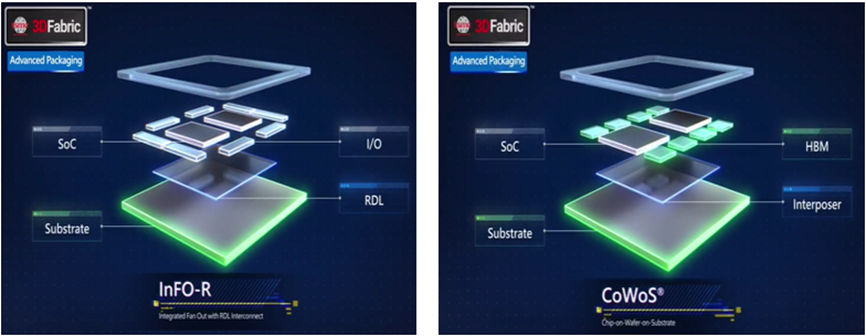

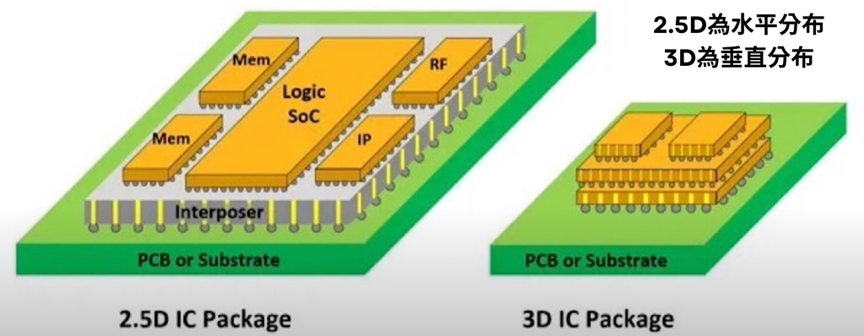

目前先進封裝技術可分為 2D 的 InFO(扇出型封裝)、2.5D 的 CoWoS(Chip on Wafer on Substrate),以及 3D 的 SoIC(System-on-Integrated-Chips)。

其中 InFO 技術最成熟也最便宜,約佔其先進封裝產能 70~80%(每年 8~10 萬片),並已大量使用在 Apple 的 A 系列及 M 系列晶片。

而3D的SoIC在良率上充滿挑戰,因為需要晶片與晶片完全接合,考驗晶片表面平整度,所以目前普遍度還不高。

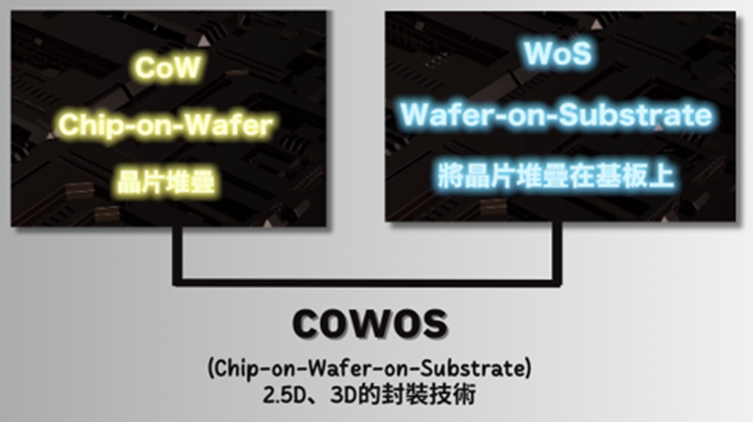

在CoWoS部分,其中Chip on Wafer(CoW)指的是直接在晶圓上進行封裝,由於這種技術更適合晶圓廠來做,因此台積電大部分的先進封裝只能靠自己做。

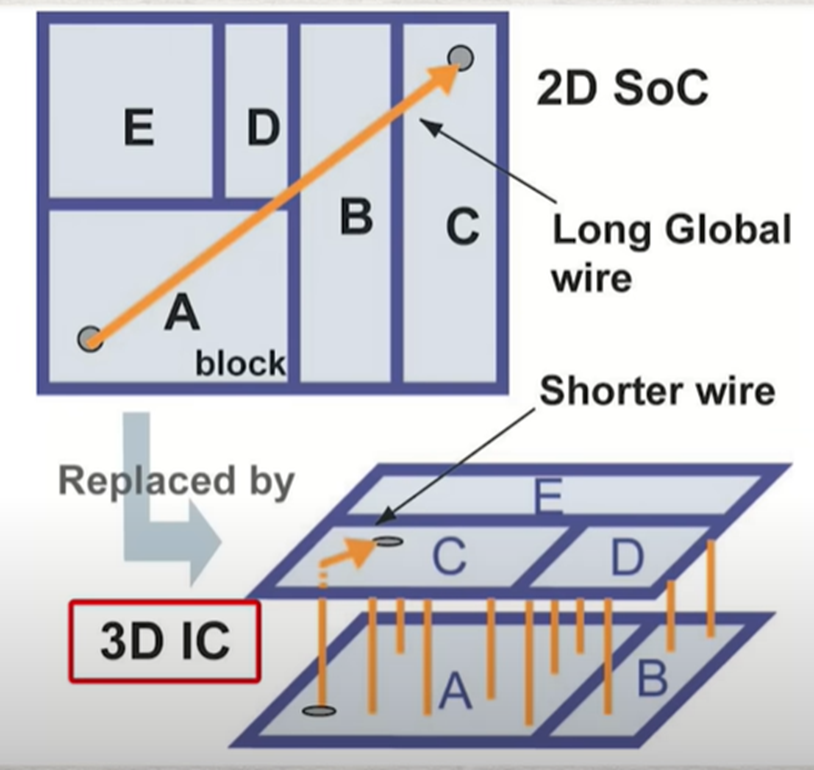

在過去傳統2D封裝如chiplet,就像員工散佈在各大城市裡,訊號之間的傳遞,需要通過許多路徑,增加耗損且托慢速度。

而cowos堆疊技術就像員工都住在同一棟大樓中,資料訊號傳遞靠上下電梯直達即可,達到高速傳輸且還能降低成本與功耗。

可以想像成原本傳統2D封裝由A到C需要穿越整個基板,3D封裝A至C點能夠以最短距離呈現,達到最高效率。

另外3D與2.5D封裝差異就在於,為了達到垂直堆疊,必須直接在晶片上做矽穿孔,而因為晶片已經被台積電做的非常小,還要在裡面做穿孔讓上下能夠流通,只有台積電自己才做得到。

圖片來源:Ansys

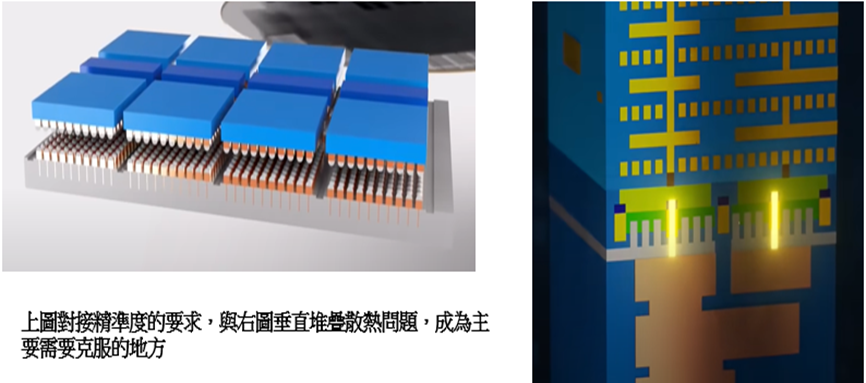

3D垂直整合封裝雖然有許多好處,但背後必定有許多需要克服的地方,像是垂直堆疊技術需要上下精準對接,只要一個細小的連接點沒有對準,便會造成成本耗損。

另外在散熱方面,由原本擴散式的分布,變成路徑更短的垂直方式,彼此距離變的更擠,運作時整個晶片猶如一團火爐,因此散熱成為需要克服的重點。

而2022年台積電成立了3D Fabric封裝大聯盟,主要整合各種不同封裝技術以因應各種不同的需求,而聯盟彼此封裝技術還能互相搭配,讓晶片效率最佳化,也成為此聯盟的目標。